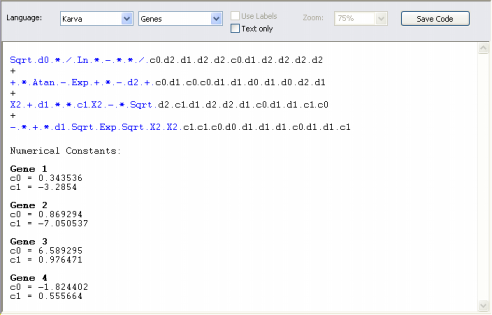

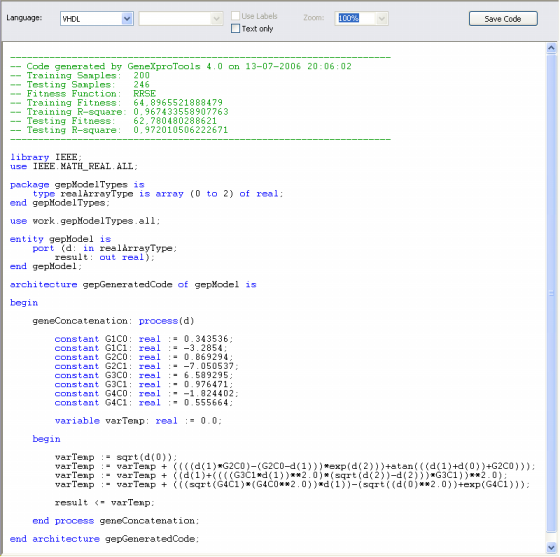

| For mathematical models, GeneXproTools 4.0 uses the VHDL

Math

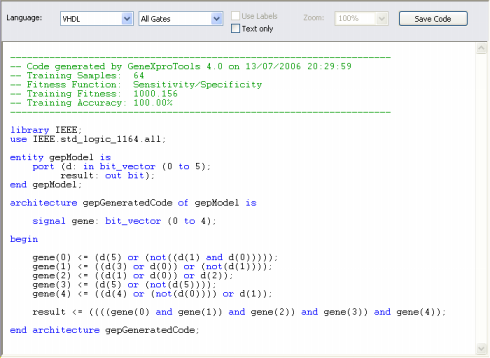

grammar to generate VHDL code from its native Karva code, whereas for Logic

Synthesis problems, GeneXproTools 4.0 uses the basic Boolean All

Gates VHDL grammar.

You can translate not only all the evolved models but also exogenous models introduced through the

Change Seed window

into VHDL. The code can then be copied to the clipboard or saved to disk. This code can be freely distributed in source or binary form.

And to translate your logic circuits into VHDL, on the GeneXproTools modeling environment, select the Model Panel, and then select both VHDL and All Gates on the Language list boxes.

|